### Chapter Six- 1st Half Pipelined Processor Delayed Controls, Hazards

EE3055 Web: www.csc.gatech.edu/copeland/jac/3055-05

# Properties a subset of states in the right of the operation of the states in the right of the states i

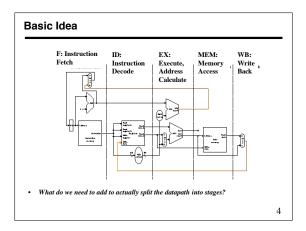

# Pipelining

- What makes it easy

- all instructions are the same length

- just a few instruction formats

- memory operands appear only in loads and stores

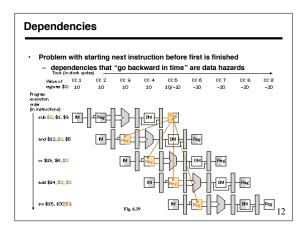

- What makes it hard?

- structural hazards: suppose we had only one memory

control hazards: need to worry about branch instructions

- data hazards: an instruction depends on a previous instruction

- + We'll build a simple pipeline and look at these issues

- We'll talk about modern processors and what really makes it hard:

\_ exception handling

\_ trying to improve performance with out-of-order execution, etc.

3

1

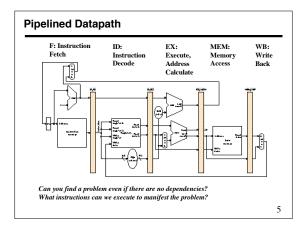

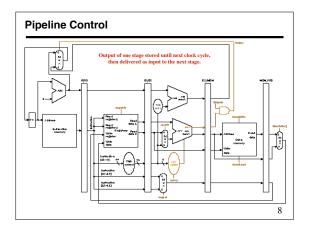

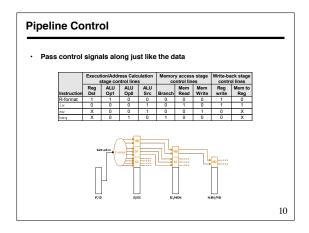

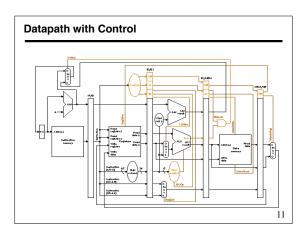

# **Pipeline control**

- We have 5 stages. What needs to be controlled in each stage?

Instruction Fetch and PC Increment

- Instruction Decode / Register Fetch

- ExecutionMemory Stage

- Write Back

- How would control be handled in an automobile plant?

a fancy control center telling everyone what to do?

should we use a finite state machine?

9

# Software Solution

Have compiler guarantee no hazards

Where do we insert the "nops" ?

| sub | \$2, \$1, \$3  |

|-----|----------------|

| and | \$12, \$2, \$5 |

| or  | \$13, \$6, \$2 |

| add | \$14, \$2, \$2 |

| SW  | \$15, 100(\$2) |

- Problem: this really slows us down!

- · Hardware solutions next set of slides.

13