| Name |  |

|------|--|

| GT#  |  |

Bring this homework to class on Friday March 26.

## HW-7. Finite State Machine - Circuit Design

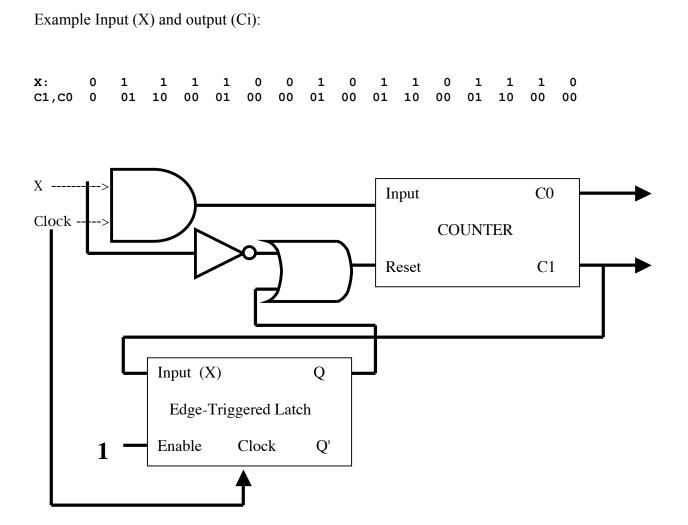

1. Design a synchronous circuit with a two-bit counter (output is C1,C0, negativeedge triggered) that counts the number of 1's in a row (from input X). When X=0, or a third "1" in a row is detected, resets the counter output, C1, C0, to 0,0.

| Name |  |

|------|--|

| GT#  |  |

2. Complete the table below. A "2M x 16" memory has 2M words of 16 bits.

| Memory    | <b>Total Bits</b> | # of addresses | # of    | # of data lines |

|-----------|-------------------|----------------|---------|-----------------|

|           |                   |                | address |                 |

|           |                   |                | lines   |                 |

| 4M x 8    | <b>32M</b>        | <b>4M</b>      | 22      | 8               |

| 1M x 32   | <b>32M</b>        | 1 <b>M</b>     | 20      | 32              |

| 128K x 16 | <b>2M</b>         | <b>128K</b>    | 17      | 16              |

| 1K x 4    | <b>4</b> K        | 1K             | 10      | 4               |

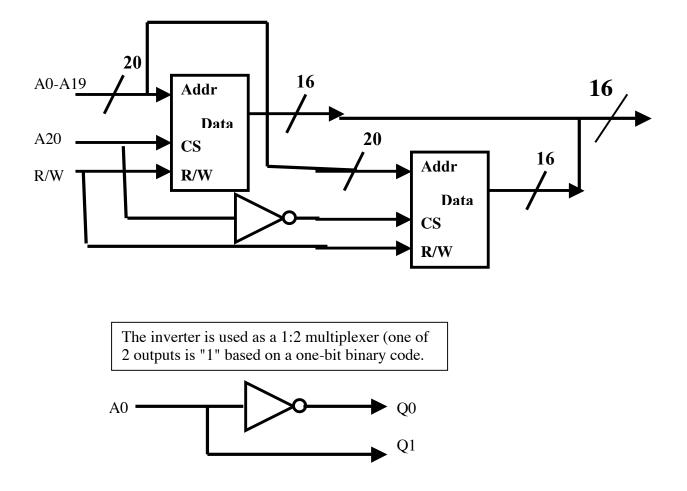

B. 3. Show how to connect these 1M x 16 chips to make a 2M by 16 memory.