Bring this homework to class on Wednesday March 3.

## HW-7. Finite State Machine - Circuit Design

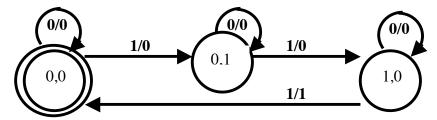

**Design the logic to implement the following FSM.** This is the state diagram for a Mealy machine with 3 states that outputs a "1" on every third "1" received as input, no matter how many "0"s are intermingled. For example:

Input: 010110100101110110110

Output: 00001000001000100010

This is the truth table for the logic that is needed. P1,P0 is the present state, Number the states such that 2\*P1 + P0 is the number of 1's seen in the present sequence of 3. N1,N0 the next state.

| P1 | P0 | Input | N1 | N0 | Output |

|----|----|-------|----|----|--------|

| 0  | 0  | 0     | 0  | 0  | 0      |

| 0  | 0  | 1     | 0  | 1  | 0      |

| 0  | 1  | 0     | 0  | 1  | 0      |

| 0  | 1  | 1     | 1  | 0  | 0      |

| 1  | 0  | 0     | 1  | 0  | 0      |

| 1  | 0  | 1     | 0  | 0  | 1      |