| SWITCH DESIGN<br>CHAPTER II-2<br>SWITCH DESIGN | <b>SWITCH NETWORKS</b><br>BASIC IDEAL SWITCH | •SWITCH NETWORKS |

|------------------------------------------------|----------------------------------------------|------------------|

| Simplest structure                             | in a computing system is a switch            |                  |

|                                                |                                              |                  |

|                                                |                                              |                  |

|                                                | IDEAL SWITCH                                 |                  |

- Path exists between INPUT and OUTPUT if Switch is CLOSED or ON

- Path does not exist between INPUT and OUTPUT if SWITCH is OPEN or OFF

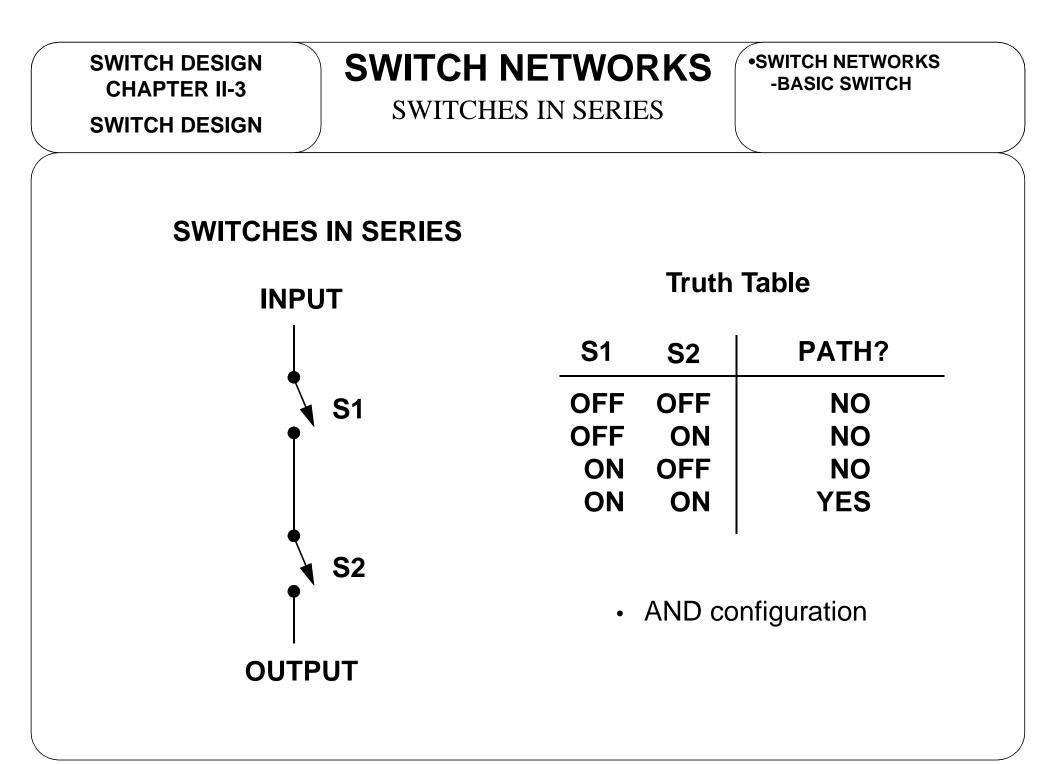

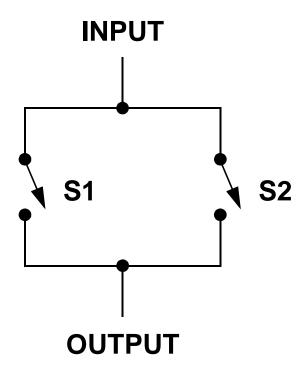

SWITCH DESIGN

## SWITCH NETWORKS

SWITCHES IN PARALLEL

•SWITCH NETWORKS -BASIC SWITCH -SWITCHES IN SERIES

### SWITCHES IN PARALLEL

| Truth Table |

|-------------|

|-------------|

| <b>S</b> 1 | <b>S</b> 2 | PATH? |

|------------|------------|-------|

| OFF        | OFF        | NO    |

| OFF        | ON         | YES   |

| ON         | OFF        | YES   |

| ON         | ON         | YES   |

|            |            |       |

OR configuration

SWITCH DESIGN

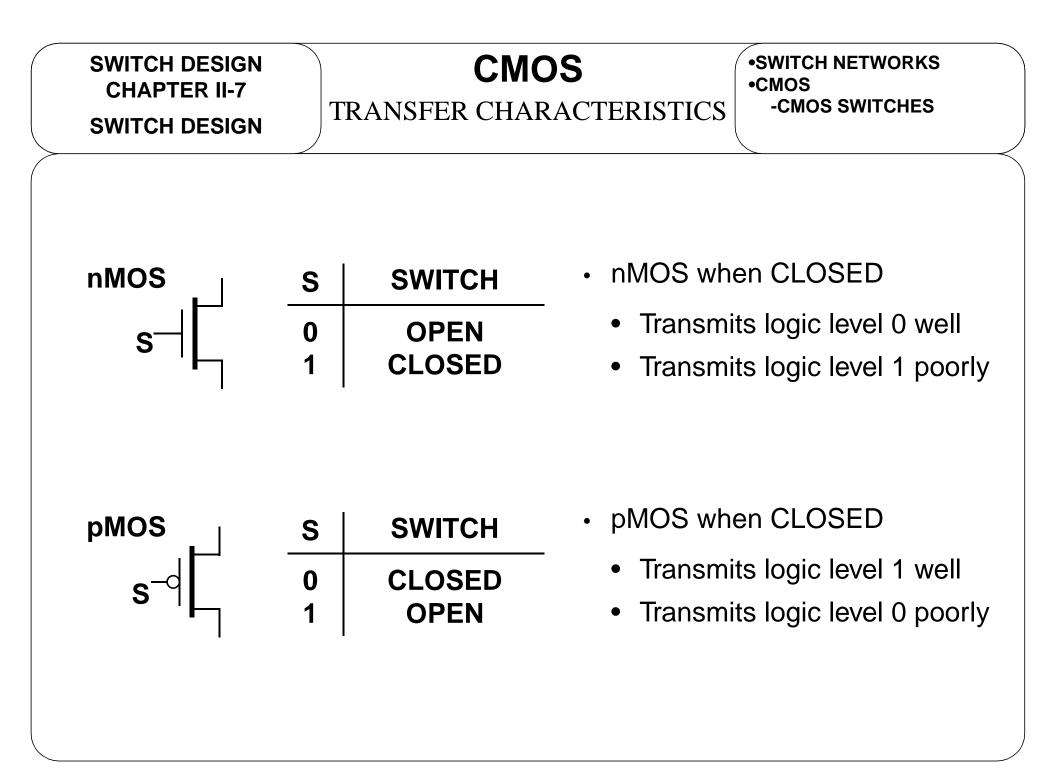

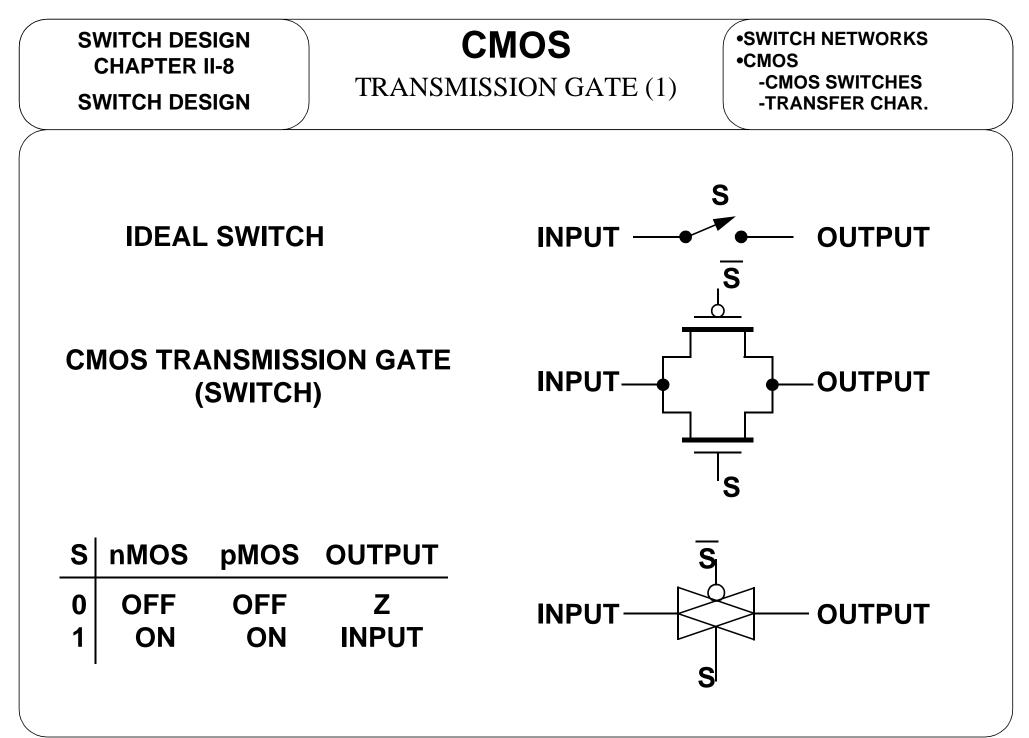

### CMOS

### CMOS SWITCHES

•SWITCH NETWORKS -SWITCHES IN SERIES -SWITCHES IN PARALLEL -INPUT SELECTOR

- The idea is to use the series and parallel switch configurations to route signals in a desired fashion.

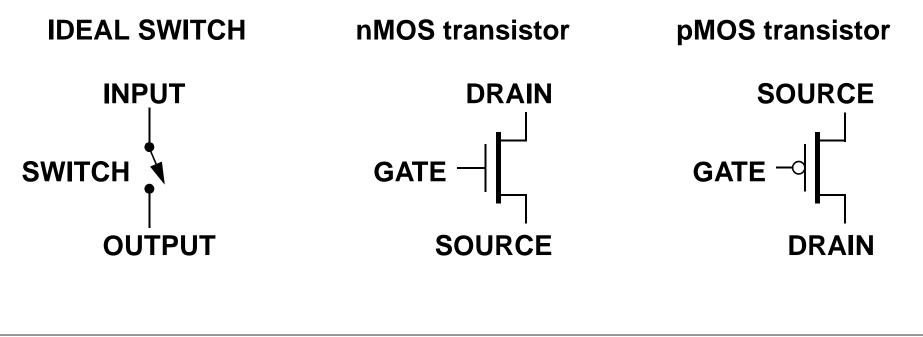

- Unfortunately, it is difficult to implement an ideal switch as given.

- Complementary Metal Oxide Semiconductor (CMOS) devices give us some interesting components.

SWITCH DESIGN

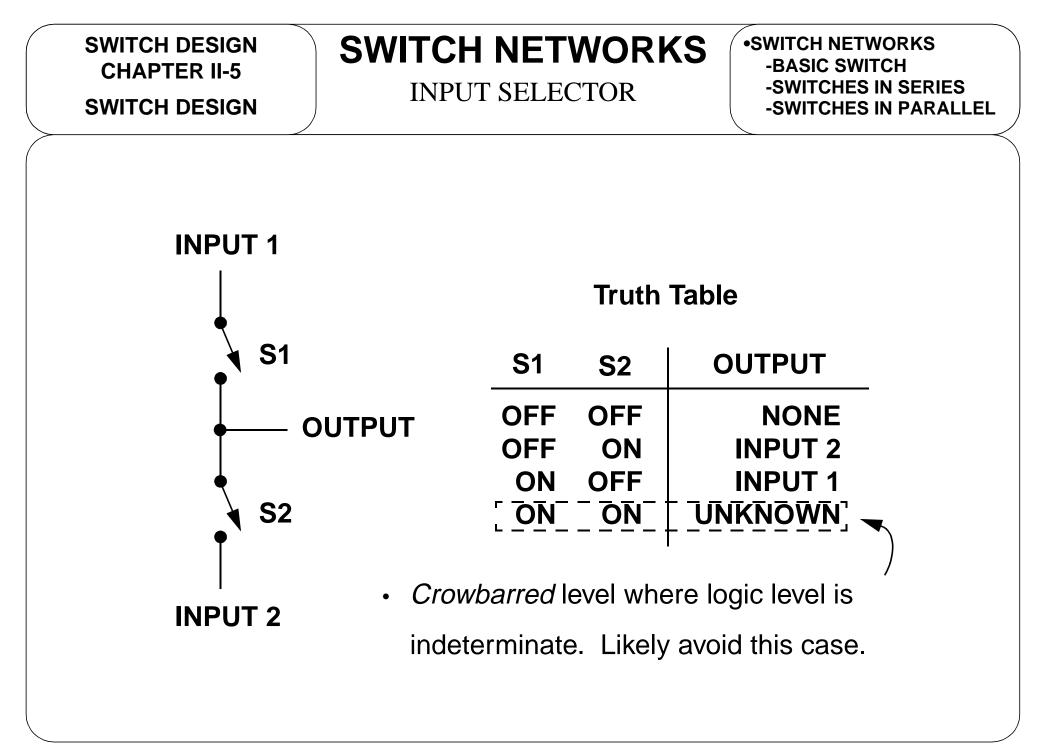

### SWITCH NETWORKS

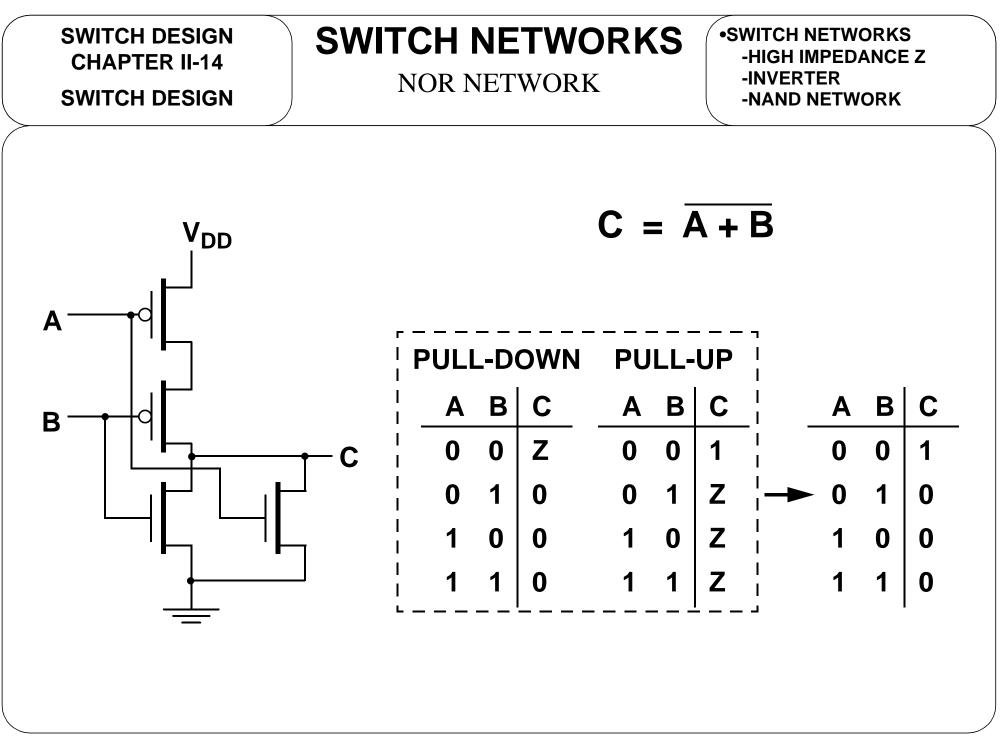

HIGH IMPEDANCE Z(1)

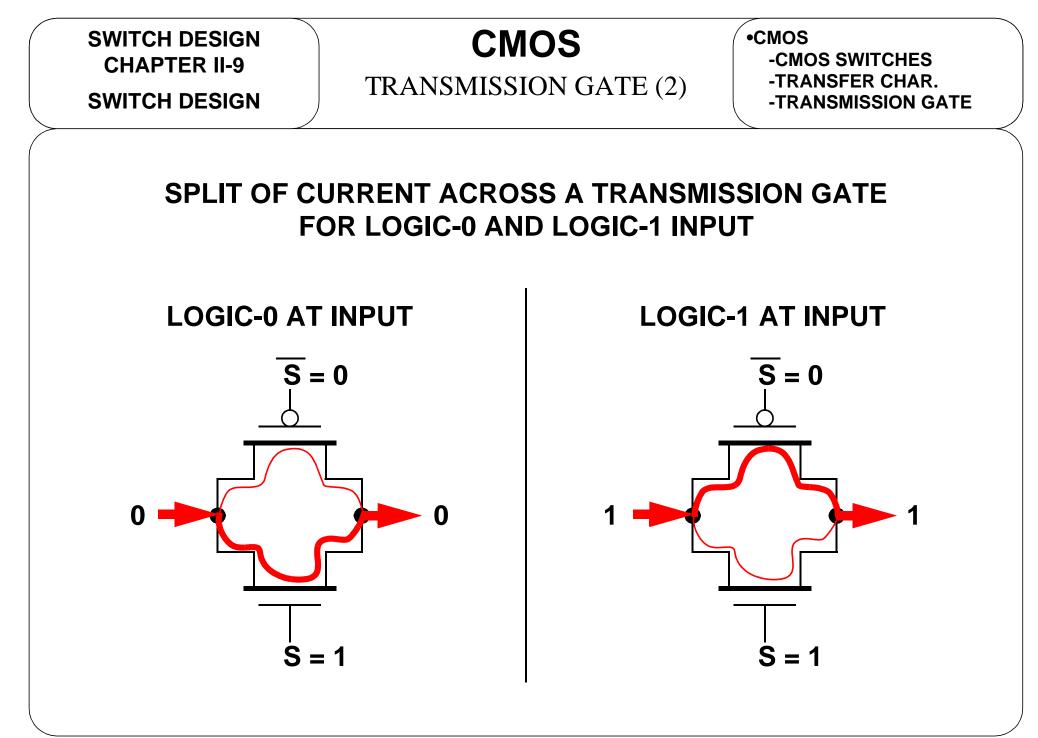

•CMOS -CMOS SWITCHES -TRANSFER CHAR. -TRANSMISSION GATE

- With switches, we can consider three states for an output:

- Logic-0

- Logic-1

- High Impedance Z

- Path exists for Logic-0 and Logic-1 when the switch is CLOSED.

S 0/1 → → → → OUTPUT = 0/1

• High impedance is a state where the switch is OPEN.

SWITCH DESIGN

### SWITCH NETWORKS

HIGH IMPEDANCE  $\mathbf{Z}(2)$

•CMOS •SWITCH NETWORKS -HIGH IMPEDANCE Z

- Another way of thinking of switches is as follows

- Path exists for Logic-0 and Logic-1 when the switch is CLOSED, meaning that the impedance/resistance is small enough to allow amply flow of current.

$1 = CLOSED \\ \times 10K\Omega$ SOURCE DRAIN SOURCE W DRAIN

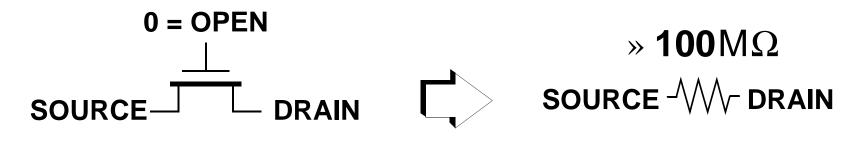

• High impedance is a state where the switch is OPEN, meaning that the **impedance/resistance is very large** allowing nearly no current flow.

R.M. Dansereau; v.1.0

R.M. Dansereau; v.1.0

D.M. Danearaau: v.1.0

R.M. Dansereau; v.1.0

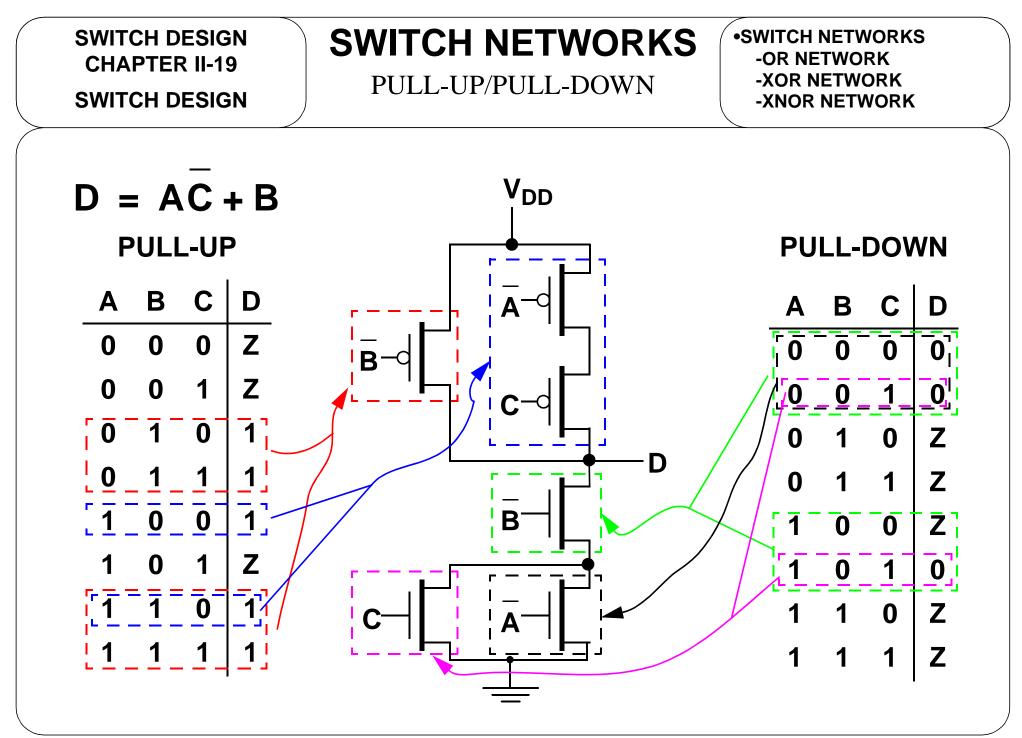

SWITCH DESIGN

# **SWITCH NETWORKS**

FUNCTION IMPLEMENTATION

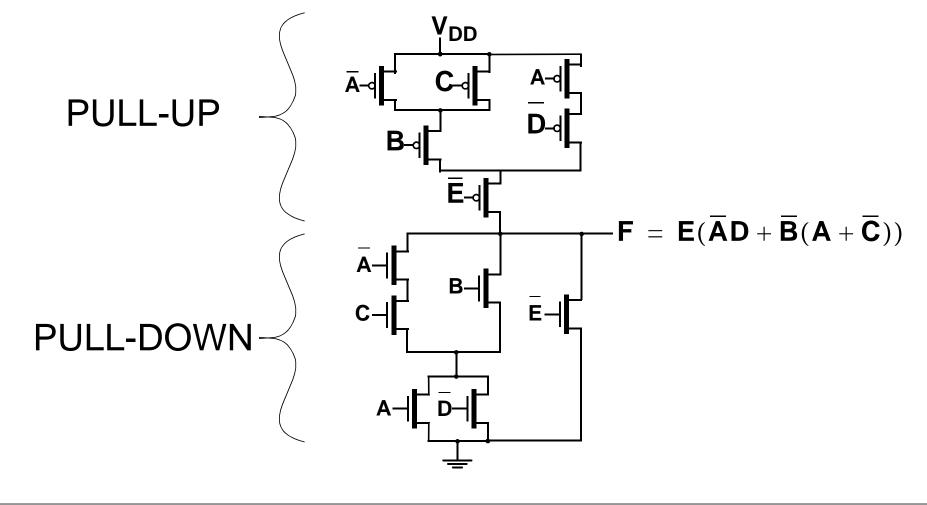

•SWITCH NETWORKS -XOR NETWORK -XNOR NETWORK -PULL-UP/PULL-DOWN

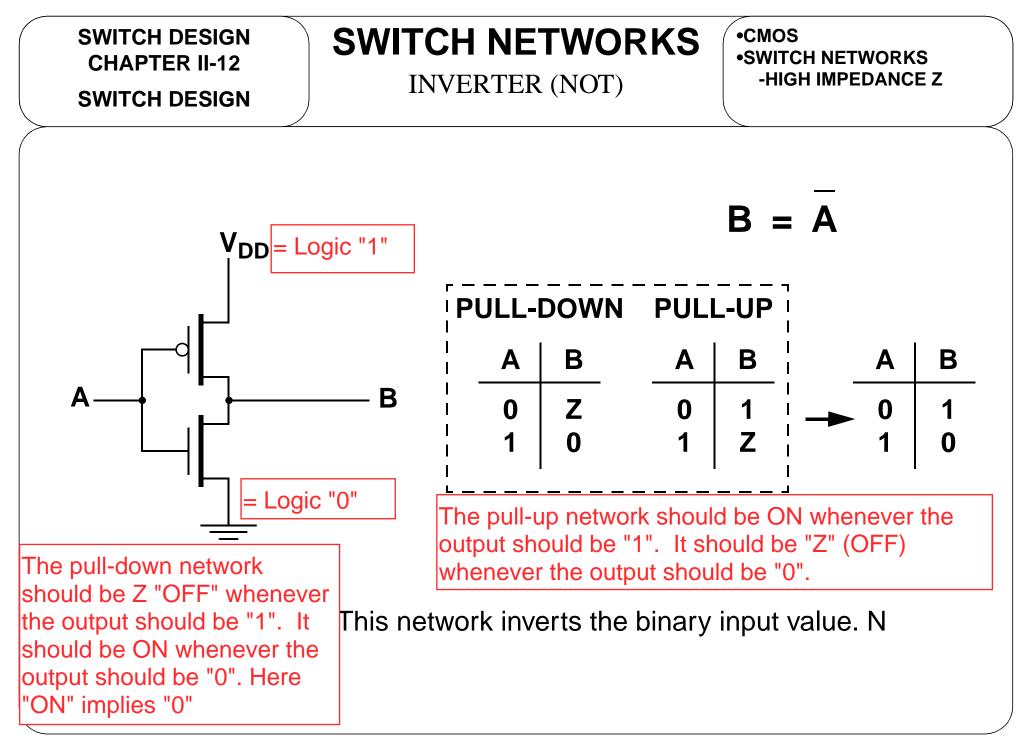

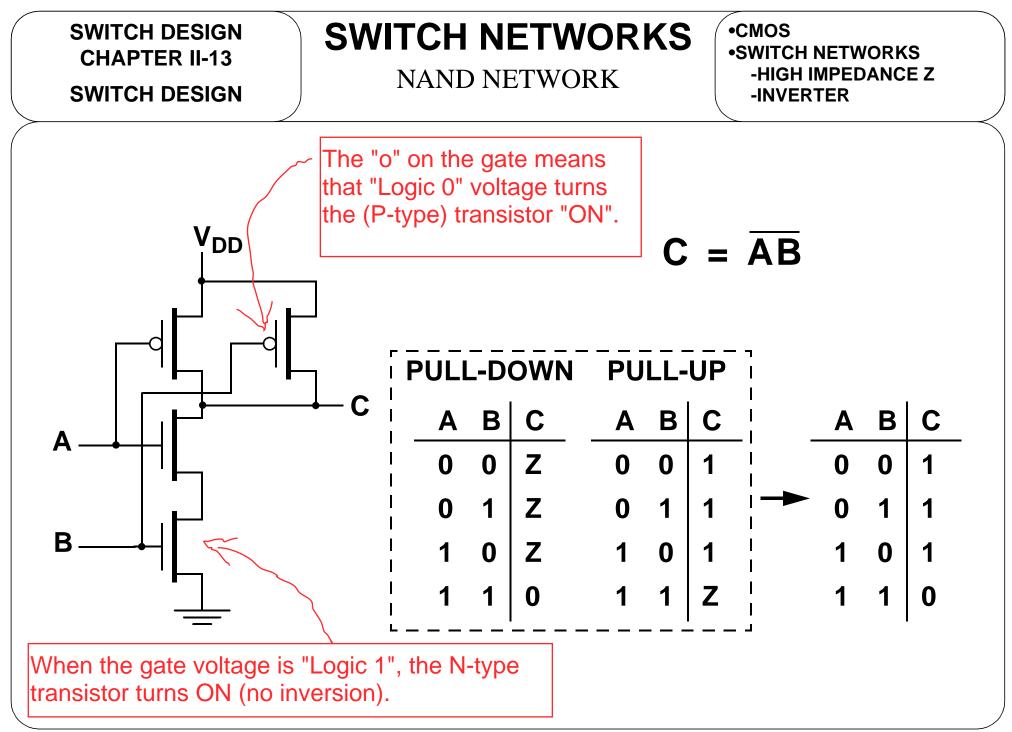

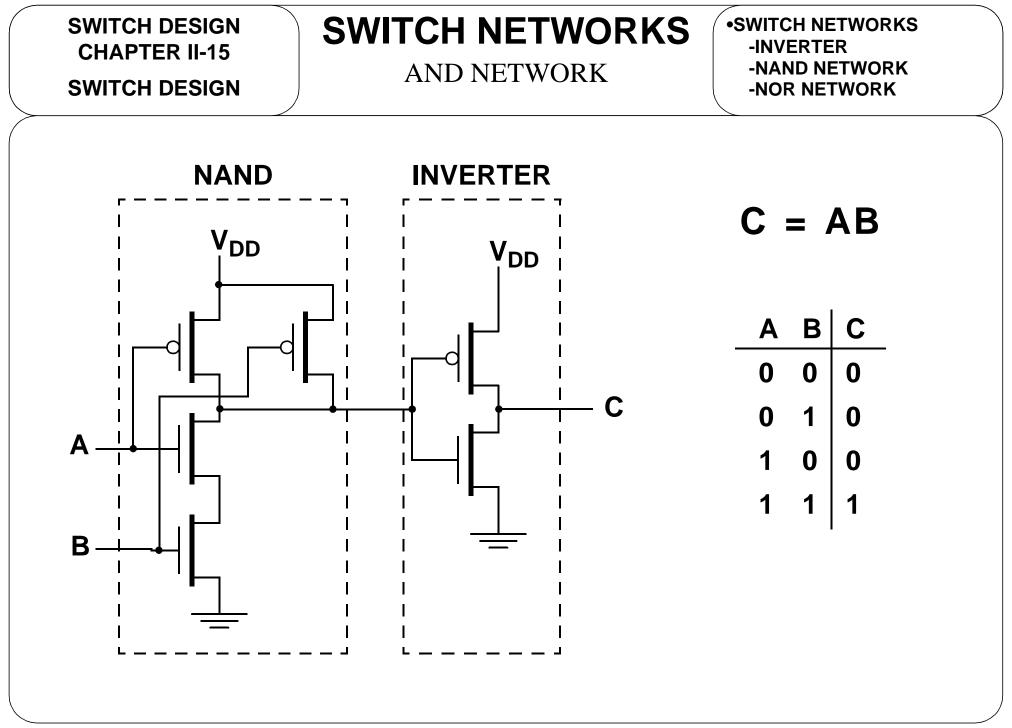

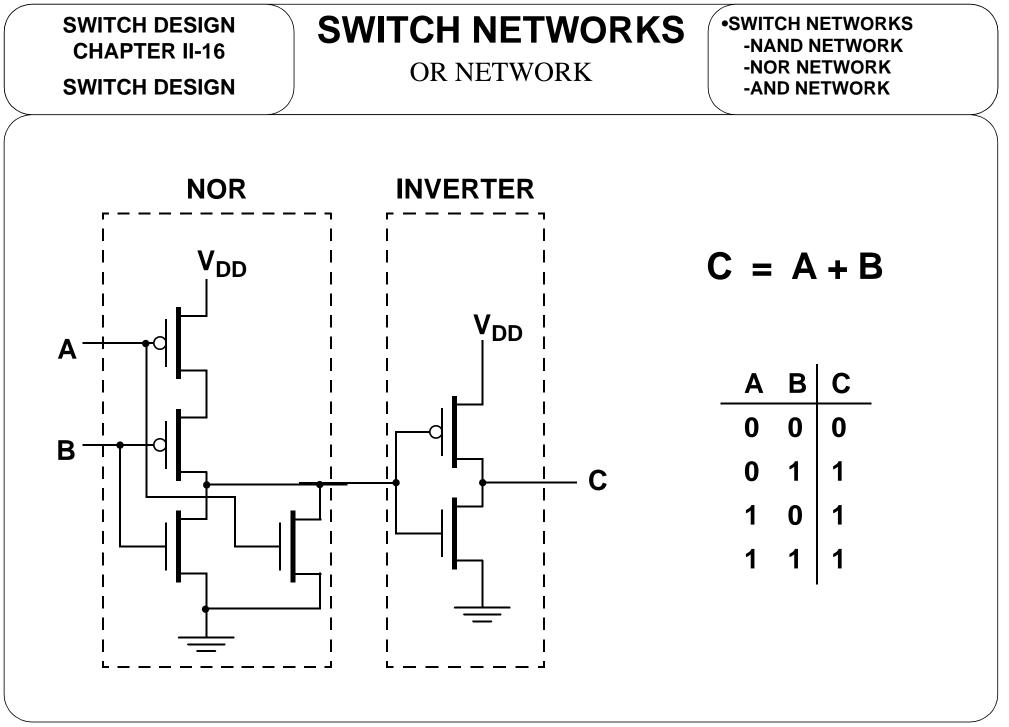

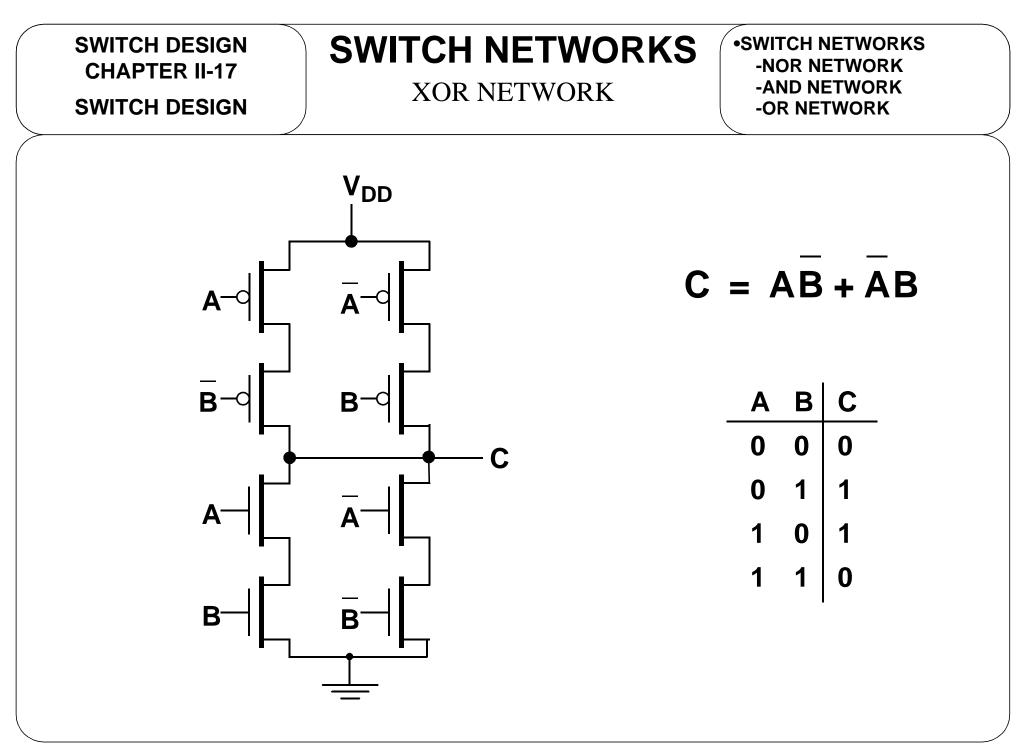

- Most Boolean functions can be easily implemented using switches.

- The basic rules are as follows

- Pull-up section of switch network

- Use complements for all literals in expression

- Use only pMOS devices

- Form series network for an AND operation

- Form **parallel** network for an **OR** operation

- Pull-down section of switch network

- Use complements for all literals in expression

- Use only **nMOS devices**

- Form **parallel** network for an **AND** operation

- Form series network for an OR operation

SWITCH DESIGN

## **SWITCH NETWORKS**

EXAMPLE PULL-UP

•SWITCH NETWORKS -XNOR NETWORK -PULL-UP/PULL-DOWN -FUNC. IMPLEMENTATION

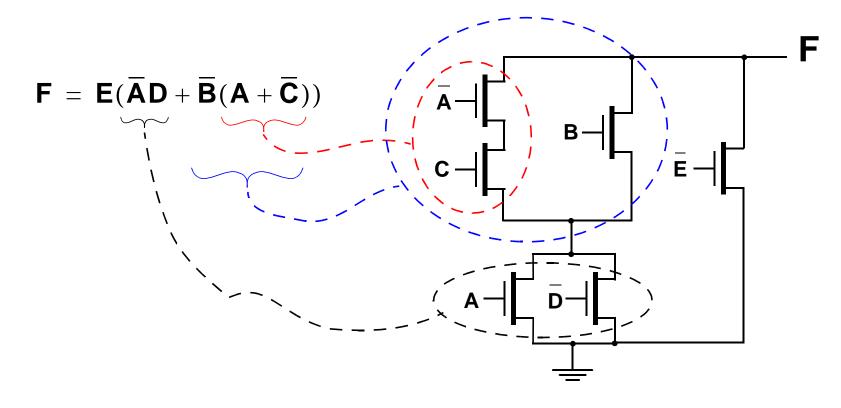

To implement the Boolean function given below, the following pull-up network could be designed.

SWITCH DESIGN

## **SWITCH NETWORKS**

EXAMPLE PULL-DOWN

•SWITCH NETWORKS -PULL-UP/PULL-DOWN -FUNC. IMPLEMENTATION -EXAMPLE PULL-UP

• To complete the switch design, the pull-down section for the Boolean

function must also be designed.

• Notice how AND and OR become OR and AND circuits, respectively.

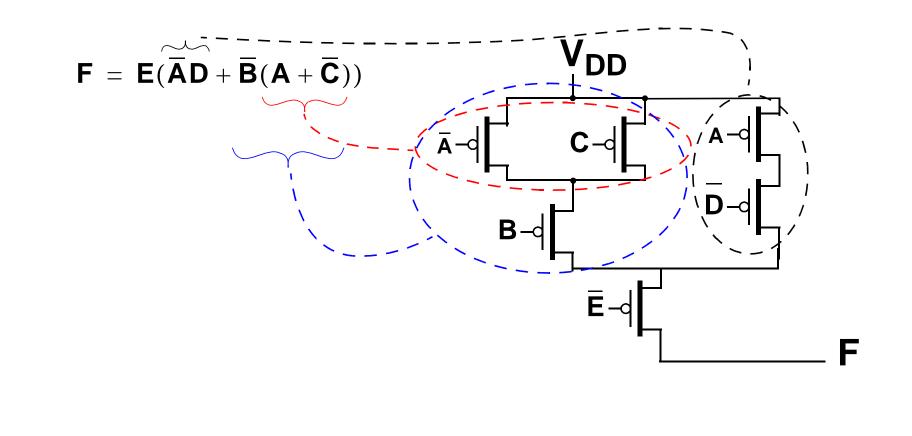

SWITCH DESIGN

### **SWITCH NETWORKS**

COMPLETED EXAMPLE

•SWITCH NETWORKS -FUNC. IMPLEMENTATION -EXAMPLE PULL-UP -EXAMPLE PULL-DOWN

Putting the pull-up and pull-down pieces together gives the following

CMOS switch implementation of the Boolean function.